#### GALLIUM NITRIDE (GaN) FET ▲ GPT65Z4YMR

GaN POWER TECHNOLOGY

# GPT65Z4YMR

# 650V ▲ 130mΩ ▲ GaN FET

MGT **A** Manufacturer Group of Technology

GALLIUM NITRIDE GaN FET ▲ SMD type Normally off device Easy to drive with standard MOSFET driver Ultra-thin DFN8080 package with 0.9mm height Moisture Sensitivity Level ▲ MSL 3 Ultra-low Q<sub>RR</sub> and very robust design

# **SPECIFICATION**

| Item (T <sub>c</sub> = 25°C, unless otherwise noted) |                        | Characteristics |

|------------------------------------------------------|------------------------|-----------------|

| Operating Temperature Range                          | TJ                     | -55°C to +150°C |

| Storage Temperature Range                            | Ts                     | -55°C to +150°C |

| Drain-Source Voltage                                 | V <sub>DSS</sub>       | 650V            |

| Transient Drain-Source Voltage Note 1                | V <sub>TR(DSS)</sub>   | 800V            |

| Drain-Source On-State Resistance Note 2              | R <sub>DS(ON)TYP</sub> | 130mΩ           |

| Typical Recovered Charge Note 3                      | Q <sub>RR</sub>        | 26nC            |

| Typical Total Gate Charge                            | Q <sub>G</sub>         | 38nC            |

RoHS

REACH

HALOGEN

FREE

#### Notes

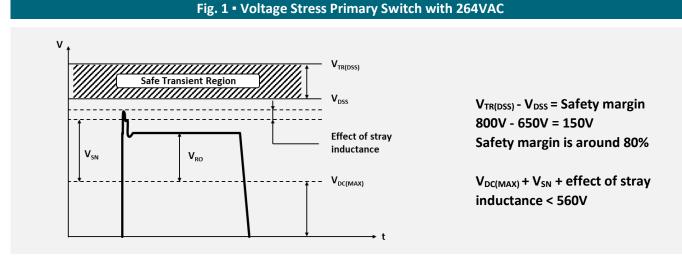

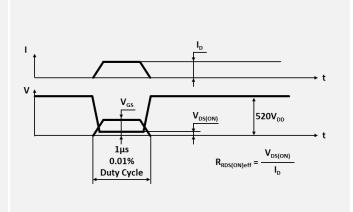

1: Spike duty cycle DC < 0.01, spike duration time < 20µs during off-state mode

2: V<sub>GS</sub> = 8V, I<sub>D</sub> = 4A, T<sub>J</sub> = 25°C

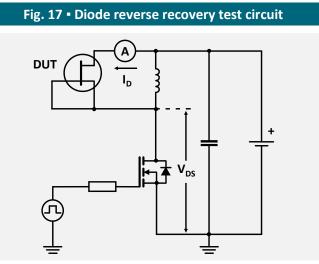

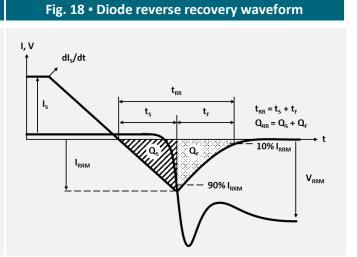

3: See diode reverse recovery test circuit and waveform, Fig. 17, and Fig. 18

# **APPLICATIONS**

| Battery  | Power      | LED      | Wireless | AC/DC     | DC/DC     | Class D Audio |

|----------|------------|----------|----------|-----------|-----------|---------------|

| Chargers | Adapters   | Lighting | Power    | Converter | Converter | Amplifiers    |

| B        | <b>P</b> - | -Ò,-     |          |           |           | <b>(</b> )    |

#### **PIN DESCRIPTION**

| Circuit Diagram | Outline - Bottom View | Pin No.     | Symbol      | Description             |

|-----------------|-----------------------|-------------|-------------|-------------------------|

| G               | 2 1                   | 1<br>2<br>3 | G<br>D<br>S | Gate<br>Drain<br>Source |

GPT65Z4YMR ▲ Rev.002 ▲ Date: 11/11/2022 ▲ Page: 1

Copyright by MGT A www.mgt.co.com A All rights reserved A The information in this document is subject to change without notice.

## **STORAGE AND HANDLING CONDITIONS**

| ESD level   | Floor life | Conditions                      | MSL |

|-------------|------------|---------------------------------|-----|

| HBM class 2 | 168 hours  | T <sub>A</sub> < 30°C, RH < 60% | 3   |

# ABSOLUT MAXIMUM RATINGS **A** T<sub>C</sub> = 25°C, unless otherwise noted

| Item                                 | Condition                                | Symbol               | Limit       | Unit |

|--------------------------------------|------------------------------------------|----------------------|-------------|------|

|                                      |                                          |                      |             |      |

| Drain-Source Breakdown Voltage       |                                          | V <sub>DSS</sub>     | 650         | V    |

| Transient Drain-Source Voltage Note1 |                                          | V <sub>(TR)DSS</sub> | 800         | V    |

| Gate-Source Voltage                  |                                          | V <sub>GSS</sub>     | ±20         | V    |

| Continuous Drain Current             | T <sub>C</sub> = 25°C <sup>Note 2</sup>  | I <sub>D</sub>       | 18          | А    |

| Continuous Drain Current             | T <sub>C</sub> = 100°C <sup>Note 2</sup> | ID                   | 11.5        | А    |

| Pulse Drain Current                  | $T_c$ = 25°C, Pulse Width = 10µs         | I <sub>DM</sub>      | 80          | А    |

| Maximum Power Dissipation            | T <sub>C</sub> = 25°C                    | PD                   | 67.5        | W    |

| Operating Temperature Range          | Case                                     | Tc                   | -55 to +150 | °C   |

| Operating Temperature Range          | Junction                                 | TJ                   | -55 to +150 | °C   |

| Storage Temperature Range            |                                          | Ts                   | -55 to +150 | °C   |

#### Note:

- 1: Spike duty cycle DC < 0.01, spike duration time < 2µs during off-state mode

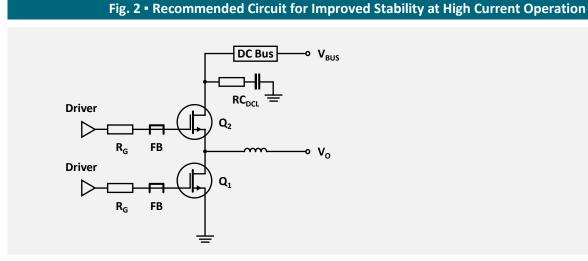

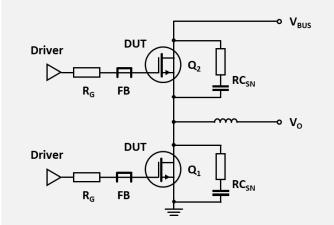

- 2: See application information for increased stability at high current operation, fig. 2

VDC(MAX)Maximum input voltageVROReflected output voltageVSNSnubber capacitor voltage

- V<sub>DSS</sub> Drain-Source breakdown voltage

- V<sub>(TR)DSS</sub> Transient Drain-source voltage

MGT 🔺 Manufacturer Group of Technology

## **APPLICATION INFORMATION**

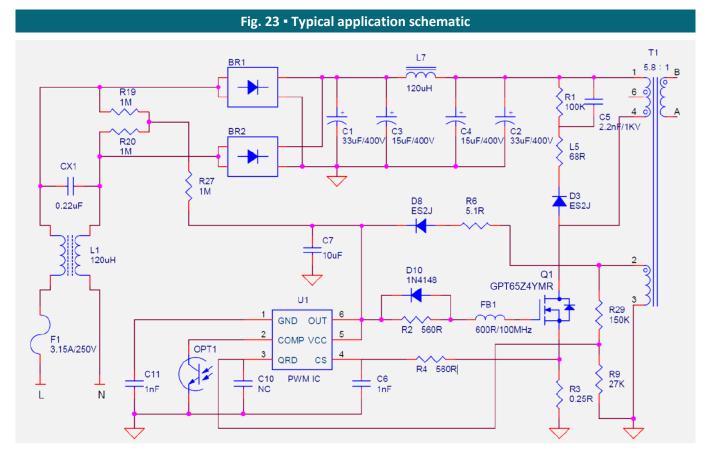

A ferrite bead (FB) should be connected in series with the gate pin to dampen the resonant circuit of gate-source loop inductance and the input capacitance of the GaN-FET. The ferrite bead should be placed as close as possible to the gate pin to minimize the gate-source loop. (See figure 2). This causes fast switching stability. We recommend an impedance of  $470\Omega$  at 100MHz for the ferrite bead. In addition, a series resistance (R<sub>G</sub>) of  $33\Omega$  should be provided.

Furthermore, a DC-link snubber should always be used to eliminate instability of the GaN-FET. In the simplest case, an RC combination is connected in parallel to the DC link bus, which significantly reduces the Q factor of any resonance in the bus. We recommend an MLCC with 68pF and an SMD resistor with  $15\Omega$  as well-suited values.

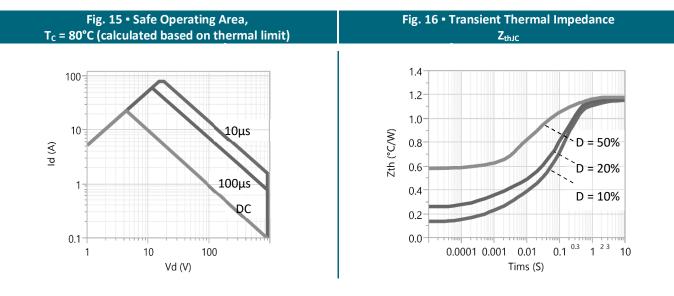

# THERMAL CHARACTERISTIC RATINGS

| Items                                         |                          | Тур.     |  |

|-----------------------------------------------|--------------------------|----------|--|

| Thermal Resistance Junction to Ambient Note 1 | <b>R</b> <sub>thJA</sub> | 50°C/W   |  |

| Thermal Resistance Junction to Case           | R <sub>thJC</sub>        | 1.85°C/W |  |

Note:

1: Device on one layer epoxy PCB for drain connection (vertical and without air stream cooling, with 6cm<sup>2</sup> copper and 70μm thickness

## **ELECTRICAL CHARACTERISTICS** A T<sub>c</sub> = 25°C, unless otherwise noted

| Item                                                   | Condition                                                                 | Symbol              | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|---------------------------------------------------------------------------|---------------------|------|------|------|------|

| Static Characteristics                                 |                                                                           |                     |      |      |      |      |

| Drain-Source Breakdown Voltage                         | $V_{GS} = OV$                                                             | V <sub>DSS</sub>    | 650  |      |      | V    |

| Gate-Source Threshold Voltage                          | $V_{GS} = V_{DS}$ , $I_D = 500 \mu A$                                     | $V_{\text{GSth}}$   | 3.5  | 4    | 4.5  | V    |

| Gate-Source Leakage Current                            | $V_{GS} = 20V, V_{DS} = 0V$                                               | I <sub>GSS</sub>    |      |      | 150  | nA   |

| Gate-Source Leakage Current                            | $V_{GS} = -20V, V_{DS} = 0V$                                              | I <sub>GSS</sub>    |      |      | -150 | nA   |

| Drain-Source Leakage Current                           | $V_{DS}$ = 650V, $V_{GS}$ = 0V                                            | I <sub>DSS</sub>    |      | 6    | 20   | μA   |

| Drain-Source Leakage Current                           | $V_{DS} = 650V, V_{GS} = 0V, T_J = 150^{\circ}C$                          | I <sub>DSS</sub>    |      | 50   |      | μΑ   |

| Drain-Source On-State Resistance                       | $V_{GS} = 8V, I_D = 4A$                                                   | R <sub>DS(ON)</sub> |      | 130  | 160  | mΩ   |

| Drain-Source On-State Resistance                       | $V_{GS}$ = 8V, $I_D$ = 4A, $T_J$ = 150°C                                  | R <sub>DS(ON)</sub> |      | 250  |      | mΩ   |

| ltem                                                   | Condition                                                                 | Symbol              | Min. | Тур. | Max. | Unit |

| Dynamic Characteristics                                |                                                                           |                     |      |      |      |      |

| Input Capacitance                                      | $V_{DS}$ = 650V, $V_{GS}$ = 0V, f = 1MHz                                  | CISS                |      | 600  |      | рF   |

| Output Capacitance                                     | $V_{DS}$ = 650V, $V_{GS}$ = 0V, f = 1MHz                                  | Coss                |      | 40   |      | рF   |

| Reverse Transfer Capacitance                           | $V_{DS}$ = 650V, $V_{GS}$ = 0V, f = 1MHz                                  | C <sub>RSS</sub>    |      | 3    |      | рF   |

| Effective Output Capacitance,<br>Energy Related Note 1 | $V_{DS}$ = 0 to 650V, $V_{GS}$ = 0V                                       | C <sub>O(ER)</sub>  |      | 25   |      | pF   |

| Effective Output Capacitance,<br>Time Related Note 2   | $V_{DS}$ = 0 to 650V, $V_{GS}$ = 0V                                       | C <sub>O(TR)</sub>  |      | 45   |      | pF   |

| Total Gate Charge                                      | $V_{\text{DS}}$ = 400V, $V_{\text{GS}}$ = 0 to 12V, $I_{\text{D}}$ = 10A  | $Q_{G}$             |      | 38   |      | nC   |

| Gate-Source Charge                                     | $V_{\text{DS}}$ = 400V, $V_{\text{GS}}$ = 0 to 12V, $I_{\text{D}}$ = 10A  | Q <sub>GS</sub>     |      | 8.5  |      | nC   |

| Gate-Drain Charge                                      | $V_{\text{DS}}$ = 400V, $V_{\text{GS}}$ = 0 to 12V, $I_{\text{D}}$ = 10A  | $Q_{GD}$            |      | 4.7  |      | nC   |

| Turn-On Delay                                          | $V_{DS}$ = 400V, $V_{GS}$ = 0 to 12V, $I_D$ = 10A, $R_G$ = 40 $\Omega$    | t <sub>D(ON)</sub>  |      | 44   |      | ns   |

| Rise Time                                              | $V_{DS} = 400V, V_{GS} = 0 \text{ to } 12V, I_D = 10A, \\ R_G = 40\Omega$ | t <sub>R</sub>      |      | 16   |      | ns   |

| Turn-Off Delay                                         | $V_{DS} = 400V, V_{GS} = 0 \text{ to } 12V, I_D = 10A, \\ R_G = 40\Omega$ | $t_{\text{D(OFF)}}$ |      | 40   |      | ns   |

| Fall Time                                              | $V_{DS}$ = 400V, $V_{GS}$ = 0 to 12V, $I_D$ = 10A, $R_G$ = 40 $\Omega$    | t <sub>F</sub>      |      | 12   |      | ns   |

| Item                                                   | Condition                                                                 | Symbol              | Min. | Тур. | Max. | Unit |

| Source-Drain Diode                                     |                                                                           |                     |      |      |      |      |

| Source-Drain Voltage                                   | $I_S = 5A$ , $V_{GS} = 0V$                                                | V <sub>SD</sub>     |      | 1.3  |      | V    |

| Jource Drain voltage                                   | I <sub>S</sub> = 10A, V <sub>GS</sub> = 0V                                | ▼ SD                |      | 1.9  |      | V    |

| Reverse Recovery Time Note 3                           | $I_{S} = 10A, V_{GS} = 0V, V_{DS} = 600V,$<br>di/dt = 1000A/µs            | t <sub>RR</sub>     |      | 16   |      | ns   |

| Recovered Charge Note 4                                | $I_{S} = 10A, V_{GS} = 0V, V_{DS} = 600V,$<br>di/dt = 1000A/µs            | Q <sub>RR</sub>     |      | 26   |      | nC   |

#### Notes:

- 1: Equivalent capacitance to give same stored energy from 0V to the stated V<sub>DS</sub>

- 2: Equivalent capacitance to give same charging time from 0V to the stated  $V_{DS}$

- **3**: See diode reverse recovery test circuit and waveform, fig. 17 and fig 18

- 4: See diode reverse recovery test circuit and waveform, fig 17 and fig. 18

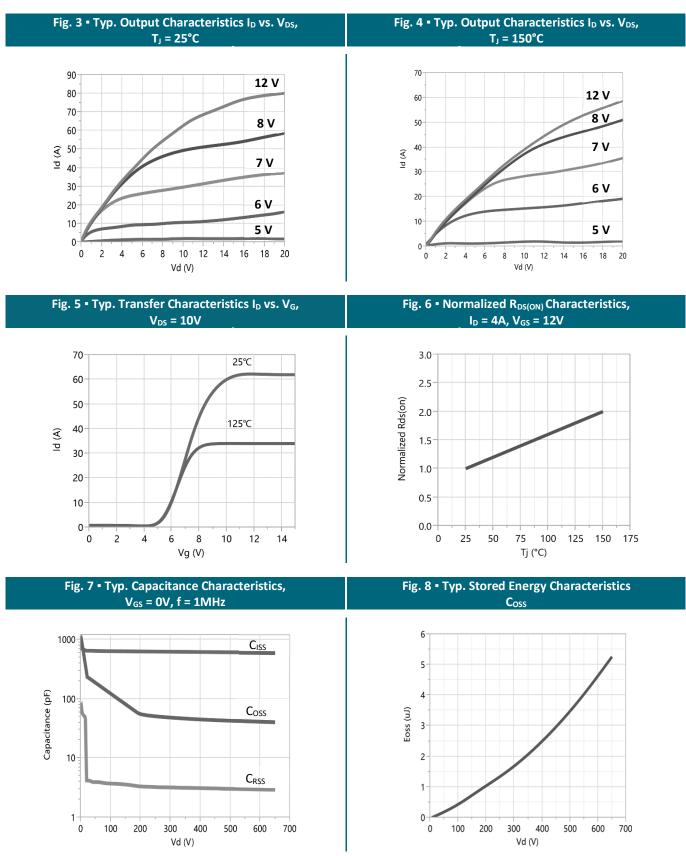

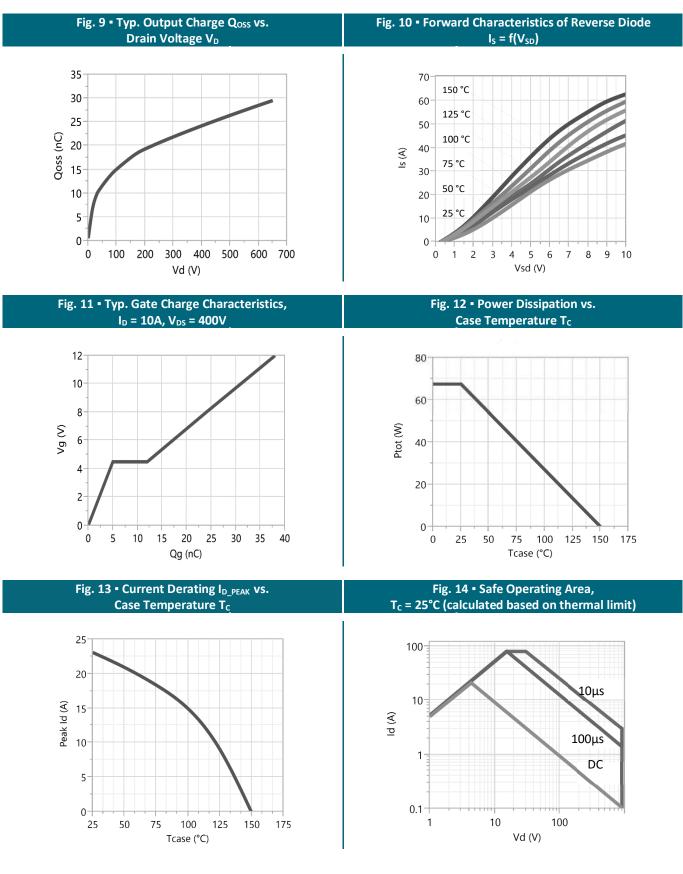

#### **REFERENCE DATA**

GPT65Z4YMR A Rev.002 A Date: 11/11/2022 A Page: 5

Copyright by MGT **A** www.mgt.co.com **A** All rights reserved **A** The information in this document is subject to change without notice.

MGT 🔺 Manufacturer Group of Technology

#### **REFERENCE DATA**

Copyright by MGT ▲ www.mgt.co.com ▲ All rights reserved ▲ The information in this document is subject to change without notice.

#### **REFERENCE DATA**

#### **TEST CIRCUITS AND WAVEFORMS**

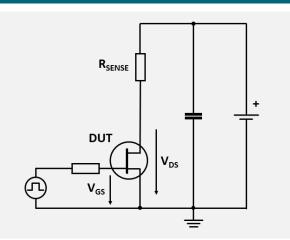

#### Fig. 19 • Switching time test circuit

Fig. 21 • Dynamic R<sub>DS(ON)eff</sub> test circuit

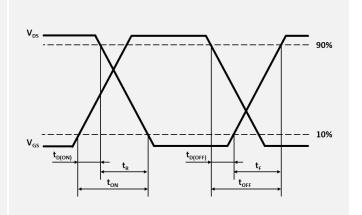

#### Fig. 20 • Switching time waveform

#### Fig. 22 • Dynamic R<sub>DS(ON)eff</sub> waveform

GPT65Z4YMR ▲ Rev.002 ▲ Date: 11/11/2022 ▲ Page: 8

Copyright by MGT A www.mgt.co.com All rights reserved The information in this document is subject to change without notice.

# LAYOUT GUIDELINES

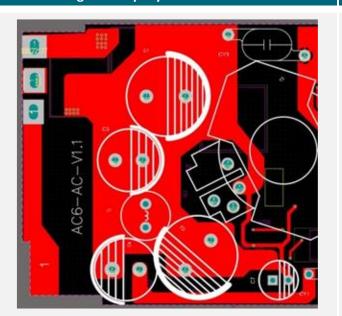

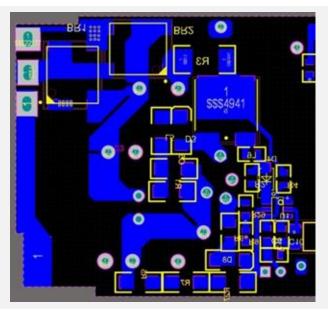

The layout of GaN FETs is very important for performance and EMI due to the GaN FETs are normally operated under high voltage and high current. Figure 24 and Figure 25 show an example of a good power layout loop:

#### Fig. 24 • Top layer for FR4 1.6mm

MGT **A** Manufacturer Group of Technology

# **POWER-LOOP INDUCTANCE**

The GaN FET has operated at a high transient current (di/dt) state. Therefore, the ringing, EMI, and voltage stress on GaN FET could be reduced by minimizing the inductance of the loop.

- 1. GND with a large area copper plane provides a low inductance ground for the GaN FET (Q1).

- 2. The power device GaN FET (Q1), diode (D3), and transformer (T1) are placed as close as possible to reduce the inductance.

- 3. The power device GaN FET (Q1) and resistor (R3) are placed as close as possible to reduce inductance and avoid abnormal switching.

- 4. Resistor (R3) and decoupling capacitor (C1) are placed as close as possible to minimize the current path and reduce the inductance.

# SWITCHING NODE CAPACITANCE

GaN devices have very low switching losses due to its low output capacitance and fast switching with high transient voltage (dv/dt). Therefore, additional capacitance on the output node should be minimized.

- 1. Shrinking the area of copper reduces the extra capacitance of the switching node.

- 2. Switching Node Trace should not overlap with Power plane and GND plane.

- 3. The copper plane of the Switching Node is not used for heat dissipation of the circuit board.

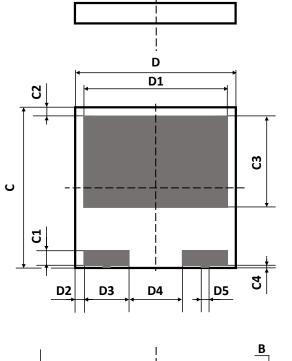

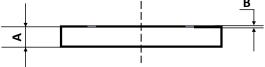

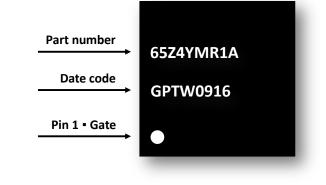

#### PACKAGE OUTLINE AND PART MARKING

| Sym | Millimeters   |

|-----|---------------|

| А   | 0.900 ± 0.050 |

| В   | 0.203 ± 0.008 |

| С   | 8.000 ± 0.050 |

| C1  | 0.800 ± 0.025 |

| C2  | 0.400 ± 0.025 |

| C3  | 4.600 ± 0.050 |

| C4  | 0.100 ± 0.025 |

# DATE CODE

| 916 |

|-----|

|     |

| 09                |                  | 1    | 6    |

|-------------------|------------------|------|------|

| Week of the Month |                  | Year |      |

|                   |                  | 16   | 2022 |

| 01                | 1 <sup>st</sup>  | 17   | 2023 |

| 02                | 2 <sup>nd</sup>  | 18   | 2024 |

| 03                | 3 <sup>rd</sup>  | 19   | 2025 |

| 04                | 4 <sup>th</sup>  | 1A   | 2026 |

|                   |                  | 1B   | 2026 |

| 52                | 52 <sup>nd</sup> |      |      |

|                   |                  | 1F   | 2031 |

| Date code: |               |  |

|------------|---------------|--|

| 09:        | e.g., week 09 |  |

| 16:        | e.g., 2022    |  |

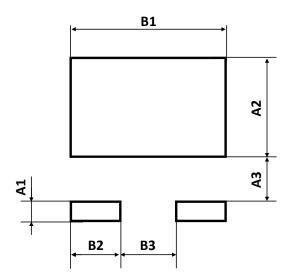

| Sym | Millimeters       |

|-----|-------------------|

| D   | 8.000 ± 0.050     |

| D1  | 7.200 ± 0.050     |

| D2  | 0.400 ± 0.025     |

| D3  | 2.300 ± 0.025     |

| D4  | 2.600 ± 0.025     |

| D5  | $0.400 \pm 0.025$ |

Copyright by MGT **A** www.mgt.co.com **A** All rights reserved **A** The information in this document is subject to change without notice.

## **RECOMMENDED PAD LAYOUT FOR DFN 8080**

| Sym | Millimeters |

|-----|-------------|

| A1  | 1.000       |

| A2  | 4.750       |

| A3  | 2.000       |

| B1  | 7.350       |

| B2  | 2.450       |

| B3  | 2.450       |

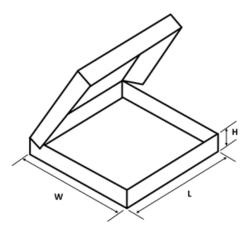

#### **ORDERING INFORMATION**

| Part Number | Package      | Packing       | Quantity | Reel Diameter |

|-------------|--------------|---------------|----------|---------------|

| GPT65Z4YMR  | Thin DFN8080 | Tape and Reel | 2 500pcs | 330mm (13")   |

#### **REEL BOX DIMENSION** All dimensions in mm

| <b>Outside Dimensions</b> |     |  |  |  |

|---------------------------|-----|--|--|--|

| Ø 330mm reel              |     |  |  |  |

| W 350                     |     |  |  |  |

| L                         | 350 |  |  |  |

| Н                         | 80  |  |  |  |

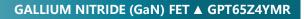

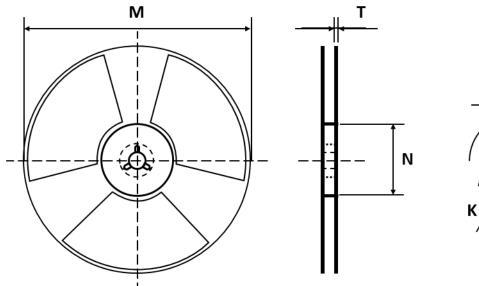

#### **REEL DIMENSIONS** All dimensions in mm

| Tape Size | Reel Size | М       | N       | т    | Н              | К     | S     |

|-----------|-----------|---------|---------|------|----------------|-------|-------|

|           |           | Ø330.00 | Ø102.00 | 2.00 | 13.00          | 10.50 | 2.00  |

| 24mm      | Ø330      | ±0.20   | ±0.10   | ±2.0 | +0.50<br>-0.20 | ±0.25 | ±0.25 |

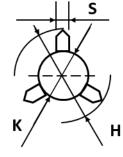

# TAPE DIMENSIONS All dimensions in mm

| Package | A0    | B0    | К0    | D0    | D1    | E     | E1    | E2    | P0    | P1    | P2    | Т     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| DFN8080 | 8.30  | 8.30  | 1.15  | 1.50  | 1.50  | 24.00 | 1.75  | 7.50  | 12.00 | 4.00  | 2.00  | 0.30  |

| DFN0000 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.30 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.10 | ±0.05 |

GPT65Z4YMR ▲ Rev.002 ▲ Date: 11/11/2022 ▲ Page: 13

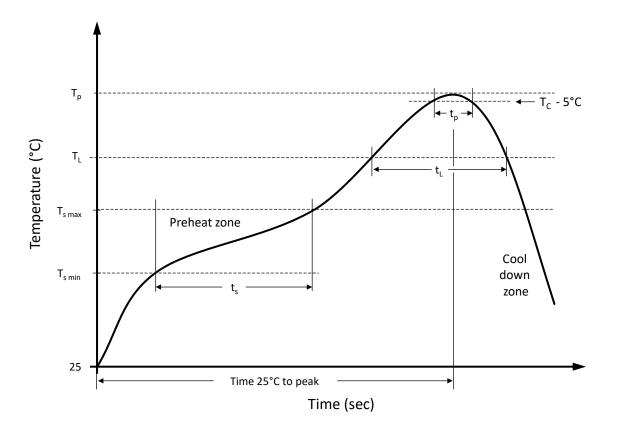

## **RECOMMENDED REFLOW SOLDERING PROFILE**

#### **Recommended reflow soldering conditions** ▲ **Refer to JEDEC J-STD-020E**

| Profile Features                                                         |                | Sn-Pb Eutetic Assembly | Pb-Free Assembly |

|--------------------------------------------------------------------------|----------------|------------------------|------------------|

| Preheat temperature min.                                                 | $T_{s min}$    | 100 °C                 | 150 °C           |

| Preheat temperature max.                                                 | $T_{s max}$    | 150 °C                 | 200 °C           |

| Preheat time $t_s$ from $T_{s min}$ to $T_{s max}$                       | ts             | 120 seconds            | 120 seconds      |

| Ramp-up rate (T₁ to Tp)                                                  |                | max. 3 °C/second       | max. 3 °C/second |

| Liquidous temperature                                                    | TL             | 183 °C                 | 217 °C           |

| Time $t_L$ maintained above $T_L$                                        | tL             | 150 seconds max.       | 150 seconds max. |

| Peak package body temperature                                            | Tp             | 235°C                  | 260°C            |

| Timeframe of within 5°C below and up to max actual peak body temperature | t <sub>p</sub> | 20 seconds max.        | 30 seconds max.  |

| Ramp-down rate $(T_L to T_p)$                                            |                | max. 6 °C/second       | max. 6 °C/second |

| Time 25°C to peak temperature                                            |                | max. 6 minutes         | max. 8 minutes   |

GPT65Z4YMR A Rev.002 A Date: 11/11/2022 A Page: 14

#### **REVISION TABLE**

| Revision | Date       | Status          | Notes                                  |

|----------|------------|-----------------|----------------------------------------|

| 001      | 12/07/2022 | Initial release | Initial publication                    |

| 002      | 11/11/2022 | Second release  | Characteristics update, Layout example |

|          |            |                 |                                        |

|          |            |                 |                                        |

|          |            |                 |                                        |

|          |            |                 |                                        |

## DISCLAIMER

Except for the written expressed warranties, MGT does not implicitly, by assumption or whatever else, warrant, under-take, promise any other warranty or guaranty for any MGT product.

All information and technical specifications made available by MGT are for guidance only and we reserve the right to change or modify them without prior notice. Unless expressly stated in writing by MGT, we reject any guarantees, obligations, or warranties.

All MGT products with the technical specifications described are suitable for use in certain applications. Operating, production, storage and environmental conditions can have a massive influence on the parameters mentioned in the data sheets, which cause the performance to vary over time.

It is subject to the user's duty of care to design and validate his products in such a way that appropriate measures are taken, such as protective circuits or redundant systems to ensure the safety standards required in the application.

MGT components are not designed or rated for use in life support, rescue, safety critical, military, or aerospace applications where failure or malfunction could result in property or environmental damage, serious injury or death. In the aforementioned cases, please contact us before using MGT products.

In principle, we reserve all rights and MGT's general terms and conditions apply. You can find them on our website <u>www.mgt.co.com.</u>